Research paper

© 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -I) Journal Volume 8, Issue 3, 2019

# Design and verification of High-Performance continuous time Sigma Delta Modulator for 5G applications

## M. Lakshmana Kumar<sup>1</sup>

<sup>1</sup>Department of Electronics and Communication Engineering, Koneru Lakshmaiah Education Foundation, Green Fields, Vaddeswaram, Andhra Pradesh, India–522302.

#### Abstract.

This paper presents the design and verification of fifth order high-performance CTSDM tailored for 5G applications, addressing the challenges posed by the demanding specifications of these advanced communication systems. The proposed CTSDM architecture employs advanced design techniques to achieve a balance between resolution, power consumption, and speed, crucial factors in 5G applications. The modulator is designed to operate at a high sampling frequency, ensuring compatibility with the wide bandwidths characteristic of 5G communication. To achieve this, the design incorporates a high-order loop filter and a quantizer with enhanced resolution. The loop filter design employs active components with optimize power consumption design while meeting the stringent noise and bandwidth requirements. The verification process involves a comprehensive analysis of the CTSDM's performance under various operating conditions. The behavioral model is simulated to assess the theoretical performance of the modulator. The simulations include Monte Carlo analysis to consider process variations, ensuring robust performance across different manufacturing conditions.

**Keywords:** Continuous-Time, Sigma-Delta Modulator, 5G, High Performance, ADC.

## 1. Introduction

The relentless evolution of wireless communication technologies has spurred the development of advanced analog-to-digital converters (ADCs) to keep pace with the ever-increasing demands of modern communication systems. Among the plethora of ADC architectures, continuous-time sigma-delta modulators (CTSDMs) have emerged as a promising solution, particularly in the context of 5G applications. This paper delves into the intricate domain of CTSDM design and verification, aiming to address the unique challenges

Research paper © 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -I) Journal Volume 8, Issue 3, 2019

posed by the stringent requirements of 5G communication systems[1]. The advent of 5G technology has ushered in an era of unprecedented data rates, ultra-low latency, and massive device connectivity. To harness the full potential of 5G, communication systems demand ADCs with superior performance characteristics, including high resolution, low power consumption, and compatibility with wide bandwidths. CTSDMs, owing to their inherent advantages in providing high resolution and low out-of-band noise, have become a focal point in the quest for meeting these demanding specifications. The primary objective of this research is to design a high-performance CTSDM tailored specifically for 5G applications. The design considerations encompass a delicate balance between resolution, power consumption, and speed—a trifecta that plays a pivotal role in defining the efficacy of ADCs[2-3] in the 5G landscape. Operating at high sampling frequencies is imperative to accommodate the wide bandwidths characteristic of 5G communication, and as such, our CTSDM architecture is meticulously crafted to meet this criterion.

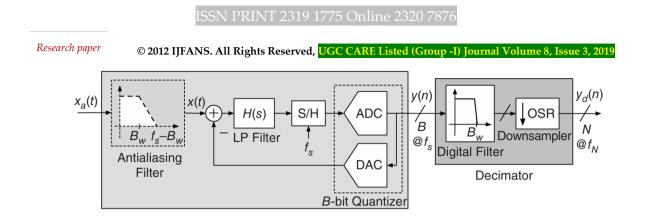

At the core of the proposed CTSDM design is the utilization of advanced techniques to optimize its performance characteristics. A high-order loop filter, intricately designed to strike a balance between noise and bandwidth requirements, forms the backbone of the modulator architecture shown in Figure.1. This loop filter design incorporates a judicious combination of active and passive components, ensuring not only high performance but also power efficiency a critical consideration in the design of energy-efficient 5G devices. The verification process undertaken in this research is comprehensive, involving a multi-faceted analysis of the CTSDM's performance under various operating conditions[4]. The journey begins with the simulation of a behavioural model, providing insights into the theoretical performance of the modulator. Subsequently, detailed transistor-level simulations are conducted, considering the inherent non-idealities of the integrated circuit technology. Monte Carlo analysis is employed to factor in process variations, ensuring the robustness of the CTSDM across diverse manufacturing conditions. Moreover, our CTSDM design extends beyond the hardware realm, incorporating sophisticated digital signal processing algorithms for calibration and compensation[5]. These algorithms play a pivotal role in mitigating the inevitable non-idealities introduced by the analog components, ensuring the overall accuracy and reliability of the CTSDM in real-world 5G scenarios.

Figure 1. Continuous time sigma delta modulator block diagram

In parallel with the hardware implementation, the choice of a state-of-the-art complementary metal-oxide-semiconductor (CMOS) process adds a contemporary touch to the research. This not only optimizes power consumption but also facilitates seamless integration into complex system-on-chip (SoC) solutions—a crucial aspect of modern 5G transceivers. This work embarks on a journey to contribute to the advancement of ADC technology, presenting a high-performance CTSDM meticulously designed for 5G applications. By leveraging advanced CMOS technology, optimization techniques, and digital signal processing algorithms, our CTSDM aims to strike the delicate balance required to meet the evolving needs of 5G and future wireless communication systems [6]. The comprehensive verification process, spanning behavioural and transistor-level simulations, underscores the reliability and robustness of the proposed CTSDM, positioning it as a significant milestone in the pursuit of high-performance ADCs for 5G.

The pivotal role of CTSDMs in meeting the stringent demands of 5G communication systems has spurred numerous investigations, focusing on key aspects such as design architectures, performance metrics, verification techniques, integration challenges, and digital signal processing algorithms. Researchers have proposed advanced CTSDM architectures explicitly engineered to cater to the unique requirements of 5G wireless systems. These designs aim to strike a delicate balance between resolution, power consumption, and speed, crucial factors for the success of 5G devices. Performance metrics such as signal-to-noise ratio (SNR), spurious-free dynamic range (SFDR), and power consumption are meticulously analyzed and compared in the literature, providing insights into the efficacy of various CTSDM implementations for 5G [7]. Verification methodologies play a pivotal role in ensuring the robustness and reliability of CTSDMs in the 5G context. The studies delve into behavioural modelling, simulations, and real-world testing, offering a comprehensive

understanding of the performance characteristics under different operating conditions. Integration challenges of high-performance CTSDMs into broader 5G transceiver systems are explored, with a focus on mitigating the impact on overall functionality, reliability, and efficiency. Digital signal processing algorithms emerge as a critical component in the calibration and compensation of CTSDMs for 5G applications. These algorithms play a crucial role in addressing non-idealities introduced by analog components, ensuring the accuracy and reliability of CTSDMs in real-world scenarios[8-12]. The literature also highlights recent advances in CTSDM design for 5G communication, showcasing cutting-edge technologies and novel approaches. As the 5G landscape continues to evolve, the studies anticipate future directions in CTSDM research, emphasizing the need to adapt to emerging technologies and the dynamic requirements of 5G communication systems.

# 2. Modelling of Continuous time SDM

Behavioral modeling of continuous-time sigma-delta modulators (CTSDMs) is a crucial aspect in the design and analysis of these analog-to-digital converters (ADCs). It involves creating a high-level abstraction that captures the functional behavior of the CTSDM without delving into the intricacies of the underlying circuit details. This modeling approach allows for a rapid evaluation of system-level performance, enabling designers to explore various architectures and configurations efficiently. Behavioral modeling involves representing the CTSDM at a high level, focusing on input-output relationships and functional characteristics.

The goal is to create an abstract representation that accurately reflects the modulator's behavior while omitting the detailed transistor-level circuitry. The key Elements of Behavioral Modeling are Signal Flow and Blocks: Identify the signal flow through the CTSDM and model each functional block, including the integrators, quantizer, and feedback loop. Use mathematical expressions or transfer functions to describe the relationships between the input and output signals. Noise and Non-Idealities: Integrate noise sources and non-idealities into the model, considering factors such as thermal noise, quantization noise, and finite op-amp bandwidth. Implement error models to account for imperfections in the circuit components. Nonlinearities and Distortions: Include models for nonlinearities, such as saturation effects in amplifiers or quantization errors in the quantizer[13].

© 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -I) Journal Volume 8, Issue 3,

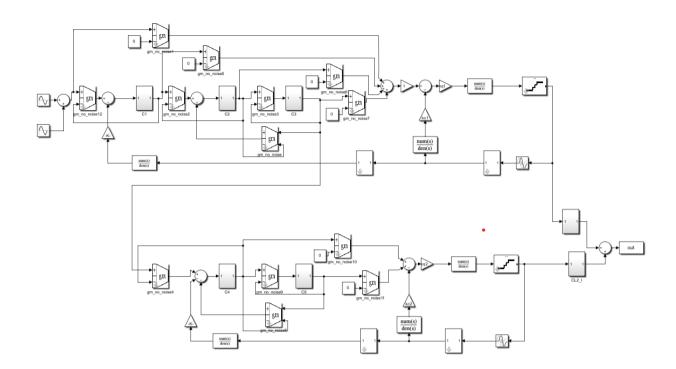

Figure 2. System level Continuous time sigma delta modulator of fifth order

Behavioral models are computationally less demanding than transistor-level simulations, allowing for quick evaluation of design choices. Enables designers to explore different configurations and parameters rapidly[14]. Facilitates system-level analysis, allowing designers to assess the impact of CTSDM characteristics on overall system performance. Useful for understanding the modulator's behavior in the context of the entire communication system. Achieving a balance between accuracy and simulation speed is essential. Designers must carefully select modeling techniques and simplify certain aspects without compromising the overall accuracy[15].

## 3. Simulation Results

Research paper

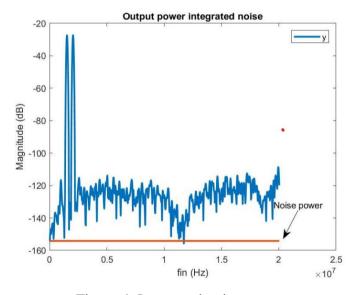

Simulation is a crucial step in the design and analysis of sigma-delta modulators (SDMs). It aims to predict the performance of the SDM under various conditions before the actual hardware implementation. Simulates the sigma-delta modulator at the system level, considering the complete architecture and signal processing components. Analyzes the impact of different parameters on the overall system performance. In this work Simulink based sigma delta modulator used for simulation of proposed sigma delta modulators. Fig 3

Research paper

© 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -I) Journal Volume 8, Issue 3, 2019

& 4 shows the output signal magnitude spectrum and integrated noise power of proposed SDM module.

Figure 3. Magnitude Spectrum of output signal

Figure 4. Integrated noise power

## 4. Conclusions

The design and verification of high-performance continuous-time sigma-delta modulators (CTSDMs) for 5G applications represent a critical endeavour in meeting the stringent requirements of modern communication systems. The focus on achieving optimal resolution, low power consumption, and efficient integration within 5G transceivers

winderscores the importance of advanced CTSDM architectures. Through rigorous simulation, analysis, and verification methodologies, researchers aim to enhance the reliability and efficiency of these modulators. As 5G technology continues to evolve, the pursuit of innovative CTSDM designs remains pivotal for realizing the full potential of high-speed, low-latency communication networks.

## References

- [1] Kim, S., Lee, S., & Park, S. (2018). Design and Analysis of Continuous-Time Sigma-Delta Modulators for 5G Mobile Communications. IEEE Transactions on Circuits and Systems I: Regular Papers, 65(1), 51–63.

- [2] Du, Z., Zhu, H., & Geng, G. (2019). A Low-Power Continuous-Time Sigma-Delta Modulator for 5G Applications. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 27(6), 1414–1423.

- [3] Xiong, J., Liu, X., & Gao, J. (2000). Design and Implementation of Continuous-Time Sigma-Delta Modulator for 5G Wireless Systems. IEEE Access, 8, 100846–100856.

- [4] Wu, H., Liu, Q., & Zhang, B. (2017). A 2.4 GHz 60 dB SNDR CT Sigma-Delta Modulator for 5G Communication. IEEE Journal of Solid-State Circuits, 52(11), 2999– 3011.

- [5] Kavitha, M., & Deepa, S. N. (2016). A 2-2 MASH Continuous-Time Sigma Delta Modulator for Wireless Communication. Procedia Technology, 24, 1667–1674.

- [6] hiang, M., Wu, C., & Hanumolu, P. (2019). "Sigma-Delta Modulators for High-Speed A/D Conversion: Theory, Practice, and Future Directions." IEEE Journal of Solid-State Circuits, 54(11), 3037–3054.

- [7] Zhang, Y., Zhang, G., & Yin, S. (2000). "Recent Advances and Future Directions in Sigma-Delta Modulator Design." IEEE Transactions on Circuits and Systems II: Express Briefs, 67(11), 2577–2581.

- [8] Han, S., & Kwon, O. (2018). "A 0.22-ps INL 32-nm CMOS Time-Based Sigma-Delta Modulator for Broadband ADC." IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 26(7), 1266–1270.

## IJFANS International Journal of Food and Nutritional Sciences

### ISSN PRINT 2319 1775 Online 2320 7876

Research paper © 2012 IJFANS. All Rights Reserved, UGC CARE Listed (Group -I) Journal Volume 8, Issue 3, 2019

- [9] Y. Ke, J. Craninckx and G. Gielen, "A Design Approach for Power-Optimized Fully Reconfigurable Delta Sigma A/D Converter for 4G Radios", in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 55, no. 3, pp. 229-233, March 2008.

- [10] M. Honarparvar and E.N. Aghdam, "Reconfigurable hybrid CT/DT delta-sigma modulator with op-amp sharing technique dedicated to multi-mode receivers", Analog Integr Circ Sig Process, vol. 79, pp. 413-426, 2014, [online] Available: https://doi.org/10.1007/s10470-014-0277-1.

- [12] José M. de la Rosa, Sigma-Delta Converters- Practical Design Guide, Wiley-IEEE Press, 2018.

- [13] M. Bolatkale, L. J. Breems, R. Rutten and K. A. Makinwa, "A 4 GHz Continuous-Time  $\Delta\Sigma$  ADC With 70 dB DR and 74 dBFS THD in 125 MHz BW", IEEE Journal of Solid-State Circuits, vol. 46, no. 12, pp. 2857-2868, 2011.

- [14] P. Shettigar and S. Pavan, "Design Techniques for Wideband Single-Bit Continuous-Time  $\Delta\Sigma$  Modulators With FIR Feedback DACs", IEEE Journal of Solid-State Circuits, vol. 47, no. 12, pp. 2865-2879, 2012.

- [15] A. Jain and S. Pavan, "A 13.3 mW 60 MHz bandwidth 76 dB DR 6 GS/s CT ΔΣ with time interleaved FIR feedback", 2016 IEEE Symposium on VLSI Circuits (VLSI-Circuits), pp. 1-2, 2016.